Overview

This was one of my first week-long labs in Computer Hardware Design, designed to introduce finite state machine concepts through an interactive adventure game. The project involved designing two communicating FSMs in SystemVerilog - one tracking the player's location through seven different rooms, and another managing whether the player possesses a sword needed to win the game.

While meant to be completed quickly as an educational exercise, this project provided solid foundations in digital design methodology, hardware description languages, and FPGA development using Quartus.

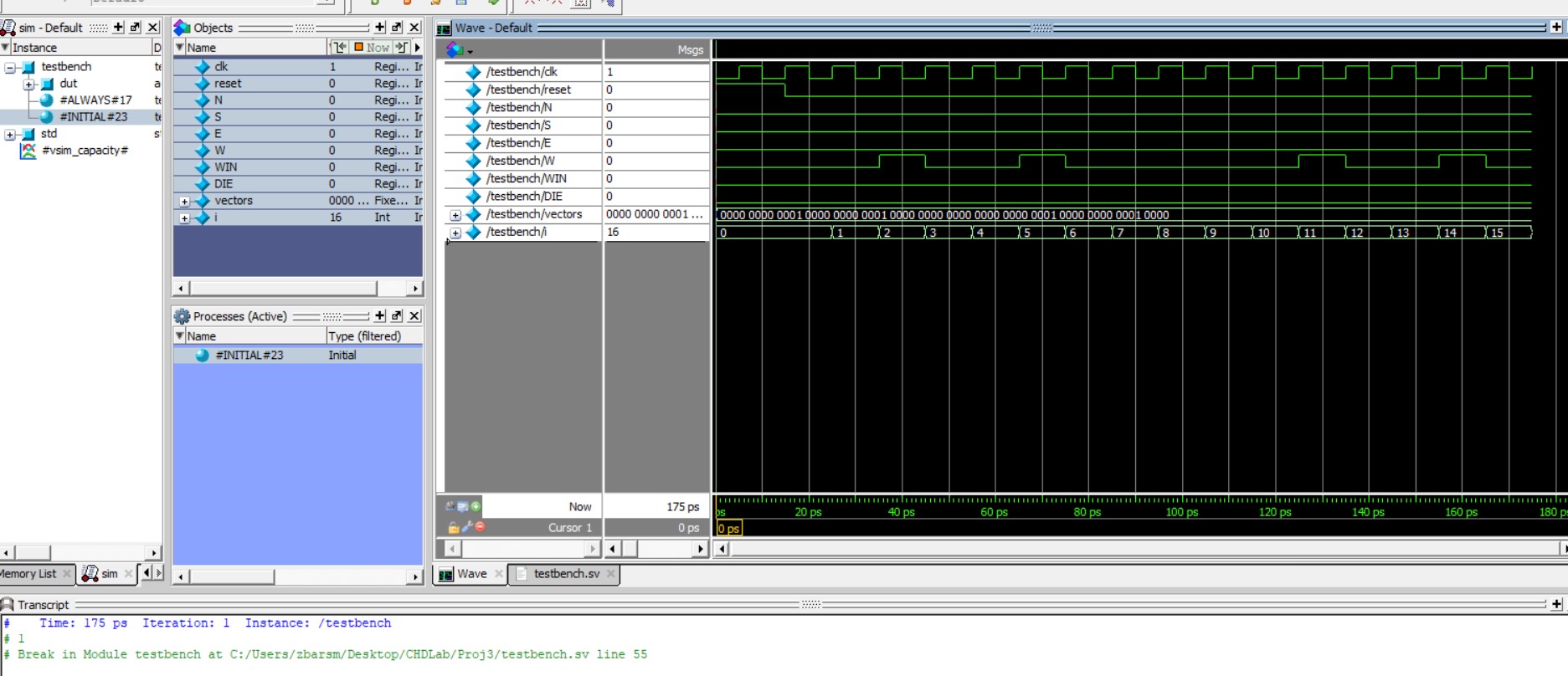

Hand-drawn state transition diagrams for room and sword FSMs

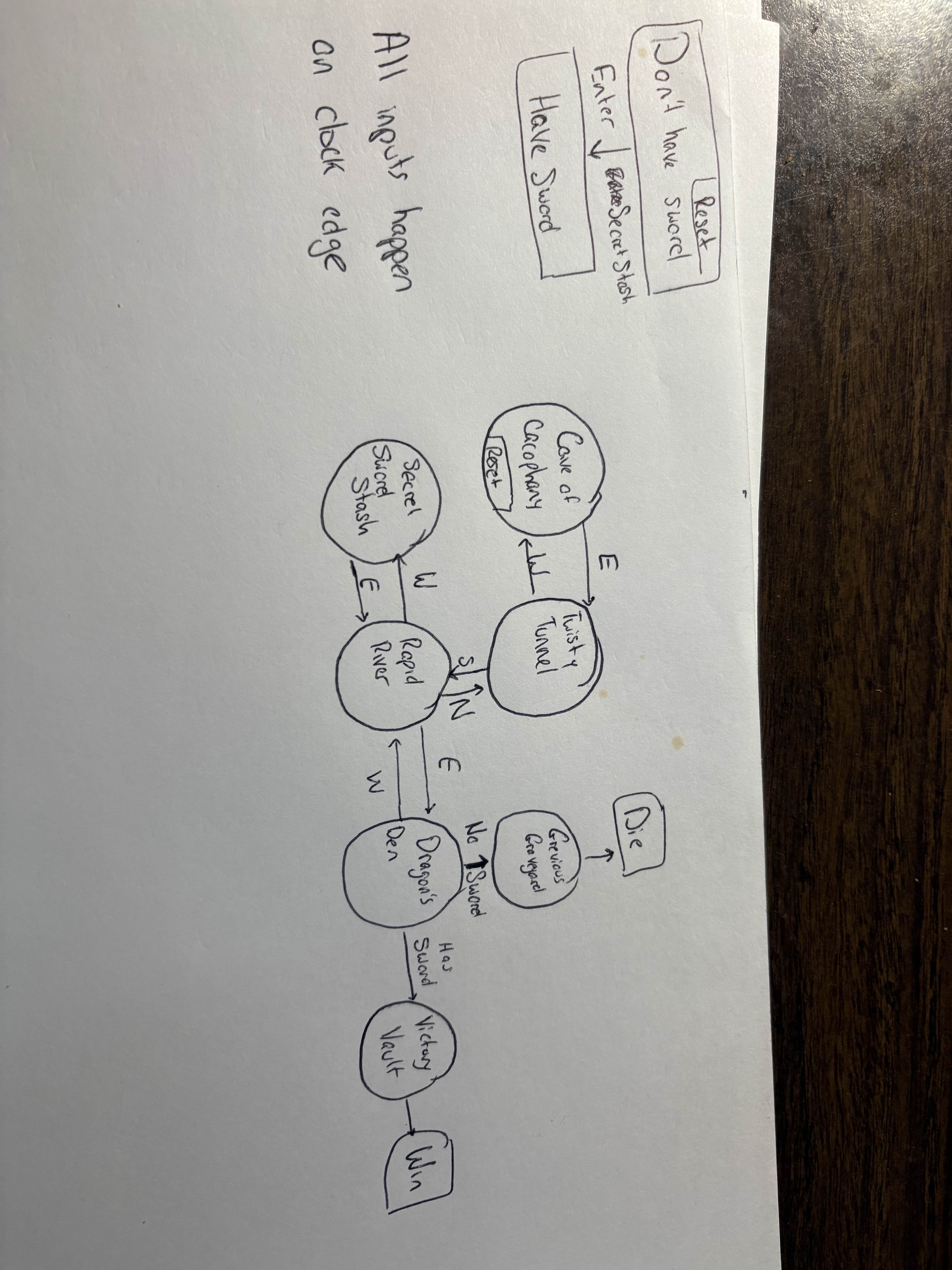

Complete RTL schematic generated by Quartus synthesis

System Design

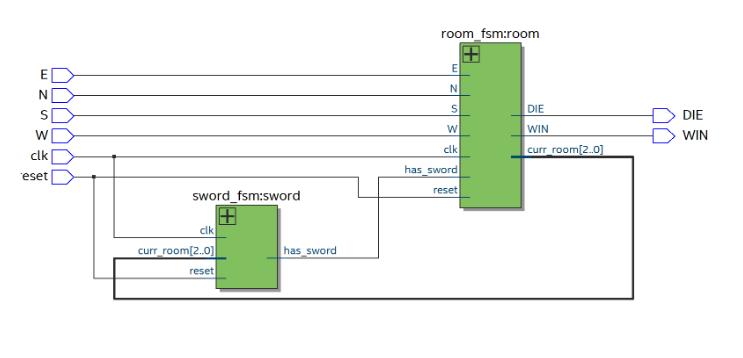

The adventure game consists of two finite state machines that communicate through shared signals. The room FSM handles player navigation through seven locations (Cave of Cacophony, Twisty Tunnel, Rapid River, Secret Sword Stash, Dragon Den, Victory Vault, and Grievous Graveyard), while the sword FSM tracks whether the player has collected the sword from the Secret Sword Stash.

The key design challenge was implementing the communication protocol between FSMs - the sword FSM monitors the current room to determine when to transition to the "has sword" state, while the room FSM checks sword possession to decide whether entering the Dragon Den leads to victory or death.

Implementation Details

The SystemVerilog implementation uses enumerated types for clear state definitions and follows standard FSM design patterns with separate always_ff and always_comb blocks. The room FSM responds to directional inputs (N, S, E, W) with appropriate state transitions based on the game map, while the sword FSM automatically transitions when the player reaches the Secret Sword Stash.

Room FSM synthesized hardware implementation

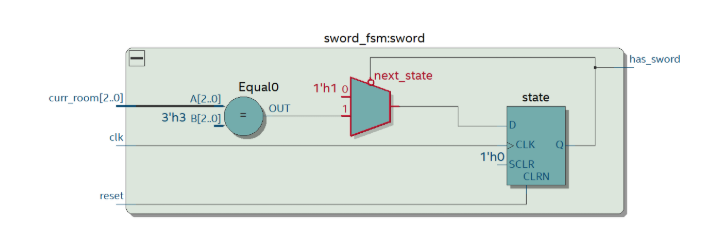

Sword FSM synthesized hardware implementation

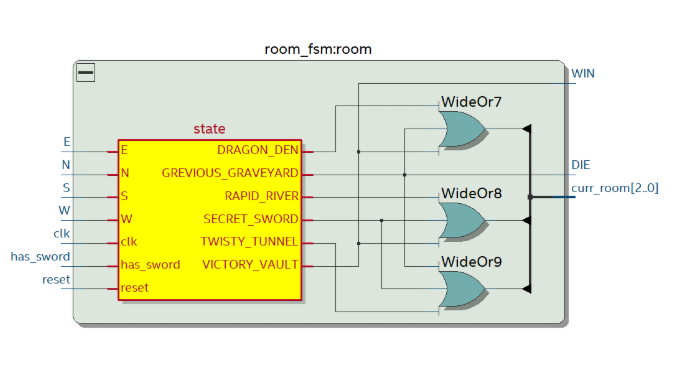

Verification and Testing

I developed a comprehensive testbench with test vectors covering both winning and losing game scenarios. The winning path (E→S→W→E→E) demonstrates collecting the sword before facing the dragon, while the losing path (E→S→E→E) shows the consequences of entering the Dragon Den without the sword. The waveform analysis confirmed correct state transitions and FSM communication.

SystemVerilog Implementation

The complete SystemVerilog implementation demonstrates clean FSM design patterns and proper module hierarchy. The code is organized into separate modules for each FSM and a top-level module that instantiates and connects them.

Results

The design successfully synthesized in Quartus and passed all verification tests. The RTL viewer confirmed the expected hardware implementation with proper state encoding and transition logic. This project provided valuable experience with digital design methodology, SystemVerilog coding practices, and FPGA development tools that formed the foundation for more complex digital systems projects.